# 192kHz Digital Audio Receiver/Converter (D/A)

### **Product Description**

MS8413 is a monolithic CMOS device that receives and decodes one of four stereo pairs of digital audio data according to the IEC60958,S/PDIF,EIAJ CP1201,or AES3 interface standards. MS8413 includes interpolation, multi-bit D/A conversion and output analog filtering. The MS8413 contains on-chip digital de-emphasis, operates from a single +3.3 V or +5 V power supply. These features are ideal for DVD players & recorders, digital televisions.

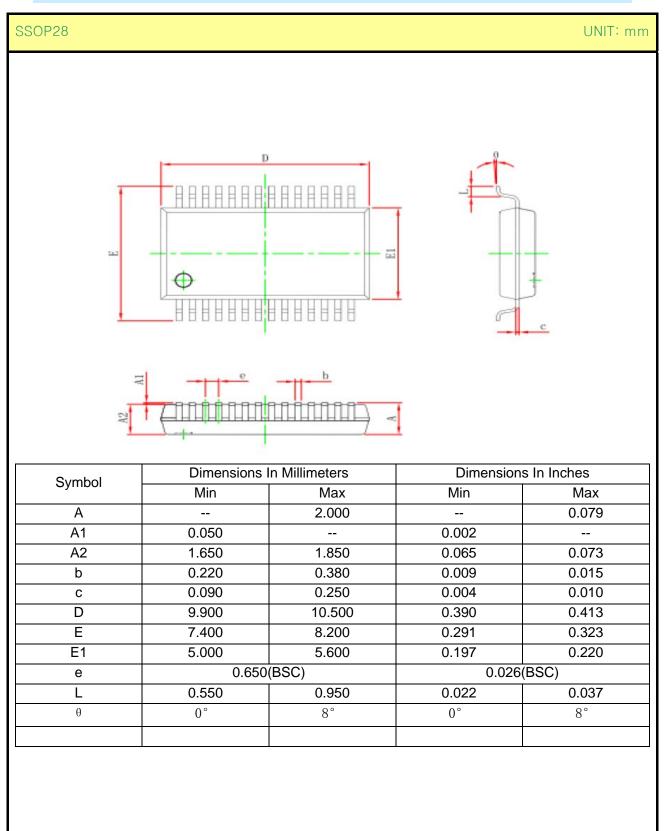

The MS8413 is available in a 28-pin SSOP package.

- Complete EIAJ CP1201, IEC-60958, AES3, S/PDIF-Compatible Receiver

- +3.3 V or +5 V Power Supply

- 4:1 S/PDIF Input MUX

- 32 kHz to 192 kHz Sample Frequency Range

- Low-Jitter Clock Recovery

- Single-ended or differential input

- Multi-bit Delta-Sigma Modulator

- 24-bit Conversion

- 105 dB Dynamic Range

- -90 dB THD+N

- Low Clock-Jitter Sensitivity

- On-chip Digital De-emphasis

#### **Package/Ordering Information**

| Part Number | Package | Marking |

|-------------|---------|---------|

| MS8413      | SSOP-28 | MS8413  |

SSOP28

### Applications

- A/V receivers

- CD-R,DVD receivers

- multimedia speakers

- digital mixing consoles

- effects processors

- set-top boxes

- computer

- automotive audio systems

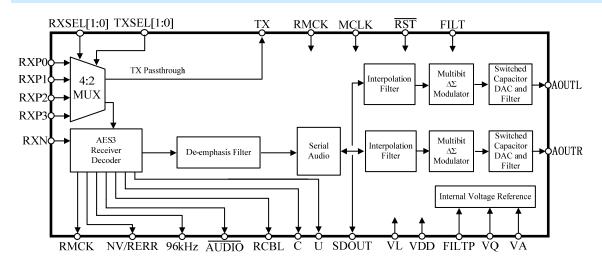

## **Block Diagram**

## 1、 CHARACTERISTICS AND SPECIFICATIONS

All Min/Max characteristics and specifications are guaranteed over the Specified Operating Conditions. Typical performance characteristics and specifications are derived from measurements taken at nominal supply voltages and  $T_A = 25^{\circ}C$ .

#### SPECIFIED OPERATING CONDITIONS

(AGND, GND = 0 V, all voltages with respect to 0 V)

| Parameter                                       | Symbol         | Min | Тур        | Max  | Units |  |

|-------------------------------------------------|----------------|-----|------------|------|-------|--|

|                                                 | VAA            |     |            |      |       |  |

| Power Supply Voltage                            | VDD            | 3.2 | 3.3 or 5.0 | 5.25 | V     |  |

|                                                 | VPLL           |     |            |      |       |  |

| Ambient Operating Temperature: Commercial Grade | т              | -10 | -          | +70  | ŝ     |  |

| Automotive Grade                                | T <sub>A</sub> | -40 | -          | +85  | C     |  |

#### ABSOLUTE MAXIMUM RATINGS

(AGND, GND = 0 V; all voltages with respect to 0 V. Operation beyond these limits may result in permanent damage to the device. Normal operation is not guaranteed at these extremes.)

| Parameter                              | Symbol           | Min  | Max   | Units |

|----------------------------------------|------------------|------|-------|-------|

| Power Supply Voltage                   | VAA,VDD,         | -    | 5.5   | V     |

|                                        | VPLL             |      |       |       |

| Input Current, Any Pin Except Supplies | I <sub>in</sub>  | -    | ±10   | mA    |

| (Note 1)                               |                  |      |       |       |

| Input Voltage                          | $V_{in}$         | -0.3 | (VDD) | V     |

|                                        |                  |      | +0.3  |       |

| Ambient Operating Temperature (power   | T <sub>A</sub>   | -55  | 125   | °C    |

| applied)                               |                  |      |       |       |

| Storage Temperature                    | T <sub>stg</sub> | -65  | 150   | °C    |

Notes:

1. Transient currents of up to 100 mA will not cause SCR latch-up.

### DC ELECTRICAL CHARACTERISTICS

| Parameters                           | _      | Symbol | Min | Тур  | Max | Units |

|--------------------------------------|--------|--------|-----|------|-----|-------|

| Power-Down Mode (Notes 2, 4)         |        |        |     |      |     |       |

| Supply Current in power-down         | VAA    | IAA    | -   | 110  | -   | μA    |

|                                      | VDD    | IDD    | -   | 70   | -   | μA    |

| VPLI                                 | L=3.3V | IPLL   | -   | 10   | -   | μA    |

| VPLI                                 | L=5.0V | IPLL   | -   | 12   | -   | μA    |

| Normal Operation (Notes 3, 4)        |        |        |     |      |     |       |

| Supply Current at 48 kHz frame rate  | VAA    | IAA    | -   | 22   | -   | mA    |

|                                      | VDD    | IDD    | -   | 6.9  | -   | mA    |

| VPLI                                 | L=3.3V | IPLL   | -   | 3.8  | -   | mA    |

| VPLI                                 | L=5.0V | IPLL   | -   | 5.2  | -   | mA    |

| Supply Current at 192 kHz frame rate | VAA    | IA     | -   | 27   | -   | mA    |

|                                      | VDD    | IDD    | -   | 23   | -   | mA    |

| VPLI                                 | L=3.3V | IL     | -   | 8.8  | -   | mA    |

| VPLI                                 | L=5.0V | IL     | -   | 12.8 | -   | mA    |

#### (AGND = GND = 0 V; all voltages with respect to 0 V.)

Notes:

2. Power-Down Mode is defined as  $\overline{RST}$  = LO with all clocks and data lines held static.

3. Normal operation is defined as  $\overline{RST} = HI$ .

4. Assumes that no inputs are floating. It is recommended that all inputs be driven high or low at all times.

#### DIGITAL INPUT CHARACTERISTICS

(AGND = GND = 0 V; all voltages with respect to 0 V.)

| Parameters                                      | Symbol          | Min  | Тур | Max  | Units |

|-------------------------------------------------|-----------------|------|-----|------|-------|

| Input Leakage Current                           | I <sub>IN</sub> | -    | -   | ±0.5 | μA    |

| Differential Input Sensitivity, RXP[3:0] to RXN | V <sub>TH</sub> | -    | 150 | 200  | mVpp  |

| Input Hysteresis                                | V <sub>H</sub>  | 0.15 | -   | 1.0  | V     |

#### DIGITAL INTERFACE SPECIFICATIONS

#### (AGND = GND = 0 V; all voltages with respect to 0 V.)

|                                                    | /               |           |           |       |

|----------------------------------------------------|-----------------|-----------|-----------|-------|

| Parameters                                         | Symbol          | Min       | Max       | Units |

| High-Level Output Voltage(I <sub>OH</sub> =-3.2mA) | V <sub>OH</sub> | (VDD)-1.0 | ) -       | V     |

| Low-Level Output Voltage(I <sub>OL</sub> =3.2mA)   | V <sub>OL</sub> | -         | 0.5       | V     |

| High-Level Input Voltage, except RXP[3:0], RXN     | V <sub>IH</sub> | 2.0       | (VDD)+0.3 | V     |

| Low-Level Input Voltage, except RXP[3:0], RXN      | V <sub>IL</sub> | -0.3      | 0.8       | V     |

### DAC ANALOG CHARACTERISTICS

( $T_A = 25^{\circ}$ C, Full-Scale Output Sine Wave, 997 Hz, Fs= 48/96/192 kHz; Test load  $R_L = 3$

| $k\Omega$ , $C_L = 10 \text{ pF}$ , Measurement Ban | dwidth 10 Hz to 20 kHz.) |

|-----------------------------------------------------|--------------------------|

|-----------------------------------------------------|--------------------------|

| Parameters                                         |               |            |    | 5V             |     |   | 3.3V |                 |     |      | Unit |          |

|----------------------------------------------------|---------------|------------|----|----------------|-----|---|------|-----------------|-----|------|------|----------|

| i arallicicis                                      |               |            |    | Min            | Ту  | p | Max  | Min             | Ty  | o M  | ax   | Unit     |

|                                                    | 18 to 24 bit  | A-weighte  | ed | 99             | 10  | 5 |      | 97              | 103 |      |      | dB       |

| Dynamic Range                                      |               | unweighted |    | 96             | 10  | 2 |      | 94              | 100 | )    |      | dB       |

| Dynamic Range                                      | 16bit         | A-weighte  | ed | 90             | 96  | 6 |      | 90              | 96  |      |      | dB       |

|                                                    |               | unweighte  | ed | 87             | 93  | 3 |      | 87              | 93  |      |      | dB       |

|                                                    | 18 to 24 bit  | 0dB        |    |                | -90 | 0 | -85  |                 | -90 | -8   | 35   | dB       |

| Total Harmonic                                     |               | -20dB      |    |                | -82 |   | -76  |                 | -80 |      | 74   | dB       |

| Distortion +                                       |               | -60dB      |    |                | -42 | 2 | -36  |                 | -40 |      | 84   | dB       |

| Noise                                              | 16bit         | 0dB        |    |                | -90 |   | -84  |                 | -90 |      | 34   | dB       |

|                                                    |               | -20dB      |    |                | -73 |   | -67  |                 | -73 |      |      | dB       |

|                                                    |               | -60dB      |    |                | -33 |   | -27  |                 | -33 |      | 27   | dB       |

|                                                    | 18 to 24 bit  | A-weighte  |    | 95             | 10  |   |      | 93              | 103 |      |      | dB       |

| Dynamic Range                                      |               | unweighte  |    | 92             | 10  |   |      | 90              | 100 | )    |      | dB       |

|                                                    | 16bit         | A-weighted |    | 86             | 96  |   |      | 86              | 96  |      |      | dB       |

|                                                    |               | unweighte  | ed | 83             | 93  |   |      | 83              | 93  |      |      | dB       |

|                                                    | 18 to 24 bit  | 0dB        |    |                | -90 |   | -82  |                 | -90 |      |      | dB       |

| Total Harmonic                                     |               | -20dB      |    |                | -82 |   | -72  |                 | -80 |      |      | dB       |

| Distortion +                                       |               | -60dB      |    |                | -42 |   | -32  |                 | -40 |      |      | dB       |

| Noise                                              | 16bit         | 0dB        |    |                | -90 |   | -82  |                 | -90 |      | 32   | dB       |

|                                                    |               | -20dB      |    |                | -73 |   | -63  |                 | -73 | -6   |      | dB       |

|                                                    |               | -60dB      |    |                | -33 |   | -23  |                 | -33 |      |      | dB       |

|                                                    | arameter      |            |    | Symbo          | I   | N | lin  | Тур             |     | Max  |      | Jnit     |

| Interchannel Isola                                 | ition (1 kHz) |            |    |                |     |   | -    | 100             |     |      | (    | dB       |

| DC Accuracy                                        |               |            |    |                |     |   |      | 0.1             |     | 0.05 | 1    | 10       |

| Interchannel Gain                                  | Mismatch      |            |    |                |     |   | -    | 0.1             |     | 0.25 |      | dB       |

| Gain Drift                                         |               |            |    |                |     |   | -    | 100             |     | -    | pp   | m∕°C     |

|                                                    | Analog Output |            |    |                |     |   |      | 0.65 11         |     |      | T    | 7        |

| Full Scale Output Voltage                          |               |            |    | VO             |     |   |      | 0.65•V          |     |      | _    | /pp      |

| Quiescent Voltage                                  |               |            | 10 | VQ             |     |   |      | 0.5•VA          | AA  |      | _    | DC       |

| Max DC Current draw from an AOUT pin               |               |            |    | DUTma<br>IOmay |     |   |      | 10              |     |      |      | uA       |

| Max Current draw from VQ<br>Max AC-Load Resistance |               |            |    | IQmax          |     |   |      | $\frac{100}{3}$ |     |      |      | uA       |

|                                                    |               |            |    | RL<br>CL       |     |   |      |                 |     |      |      | xΩ<br>nE |

| Max Load Capaci                                    |               |            |    | CL<br>Zout     |     |   |      | 100             |     |      | -    | pF       |

| Output Impedance                                   | e             |            |    | Zout           |     |   |      | 100             |     |      |      | Ω        |

## COMBINED INTERPOLATION & ON-CHIP ANALOG FILTER RESPONSE

| Paramet                            | Symbol            | Min             | Тур    | Max    | Unit    |    |

|------------------------------------|-------------------|-----------------|--------|--------|---------|----|

| Single-Speed Mode                  |                   |                 |        |        |         |    |

| Passband                           | to -0.1 dB corner |                 | 0      | -      | .35     | Fs |

| Passoana                           | to -3 dB corner   |                 | 0      |        | .4992   | Fs |

| Frequency Response 10 Hz           | to 20 kHz         |                 | -0.175 |        | +.01    | dB |

| StopBand                           |                   |                 | 0.5465 |        |         | Fs |

| StopBand Attenuation               |                   |                 | 50     |        |         | dB |

| Group Delay                        |                   | T <sub>gd</sub> |        | 10/fs  |         | S  |

|                                    | Fs=32KHZ          |                 |        |        | +1.5/+0 |    |

| Do omnhogia Error                  | Fs=44.1KHZ        |                 |        |        | +.05/-  |    |

| De-emphasis Error                  | Г\$—44.1КПZ       |                 |        |        | .25     |    |

|                                    | Fs=48KHZ          |                 |        |        | 2/4     |    |

| Double-Speed Mode                  |                   |                 |        |        |         |    |

| Passband                           | to -0.1 dB corner |                 | 0      |        | .22     | Fs |

| Passoana                           | to -3 dB corner   |                 | 0      |        | .501    | Fs |

| Frequency Response 10 Hz           | to 20 kHz         |                 | -0.15  |        | +.015   | dB |

| StopBand                           |                   |                 | 0.5770 |        |         | Fs |

| StopBand Attenuation               |                   |                 | 55     |        |         | dB |

| Group Delay                        |                   | T <sub>gd</sub> |        | 5/fs   |         | S  |

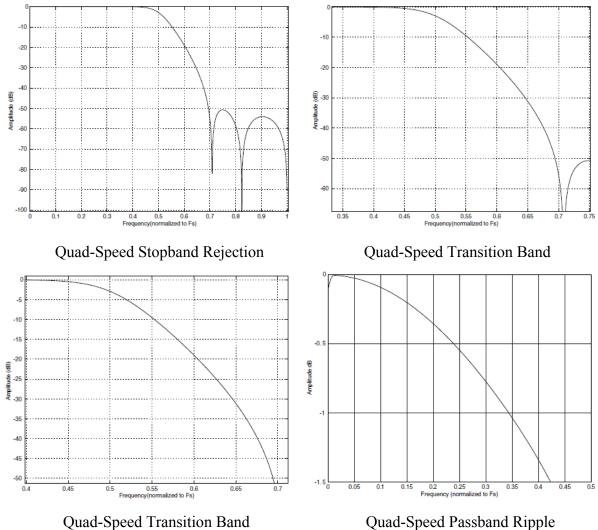

| Quad-Speed Mode                    |                   | •               |        |        |         |    |

| Passband                           | to -0.1 dB corner |                 | 0      | •      | .11     | Fs |

|                                    | to -3 dB corner   |                 | 0      |        | .469    | Fs |

| Frequency Response 10 Hz to 20 kHz |                   |                 | -0.12  |        | +0      | dB |

| StopBand                           |                   |                 | 07     |        |         | Fs |

| StopBand Attenuation               |                   |                 | 51     |        |         | dB |

| Group Delay                        |                   |                 |        | 2.5/fs |         | S  |

#### SWITCHING CHARACTERISTICS

| (Inputs: Logic 0  | = 0 V. Logic 1 =  | $VL; C_L = 20 \text{ pF})$                                        |

|-------------------|-------------------|-------------------------------------------------------------------|

| (11) 1100 20010 0 | • • • = • = • = • | $\cdot \mathbf{L}, \mathbf{C} = \mathbf{C} \mathbf{P} \mathbf{L}$ |

| Parameter                            | Symbol   | Min | Тур | Max | Units |        |

|--------------------------------------|----------|-----|-----|-----|-------|--------|

| $\overline{RST}$ Pin Low Pulse Width |          | 200 | -   | -   | μs    |        |

| PLL Clock Recovery Sample Rate       |          | 30  | -   | 200 | kHz   |        |

| MCLKOUT Output Jitter                | (Note 5) |     | -   | 200 | -     | ps RMS |

| MCLKOUT Output Duty-Cycle            | (Note 6) |     | 45  | 50  | 55    | %      |

|                                      | (Note 7) |     | 50  | 55  | 65    | %      |

Notes:

- 5. Typical RMS cycle-to-cycle jitter.

- 6. Duty cycle when clock is recovered from bi-phase encoded input.

- 7. Duty cycle when MCLKIN is switched over for output on MCLKOUT.

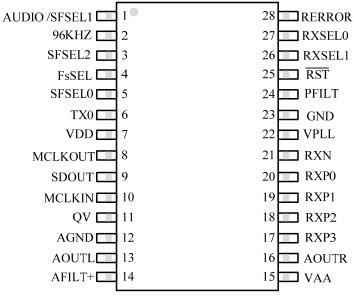

## 2、PIN DESCRIPTION

#### 2.1 MS8413 Pin Description

| Pin Name         | Pin # | Туре | Pin description                                                                                                                                                                                                   |

|------------------|-------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AUDIO<br>/SFSEL1 | 1     | I/O  | When low, a valid linear PCM audio stream is indicated.<br>This pin is also used to select the serial port format (SFSEL1) at<br>reset,must be pulled down to DGND through a 47 k $\Omega$ resistor.              |

| 96KHz            | 2     | 0    | If the input sample rate is $\leq 48$ kHz, outputs a "0". Outputs a "1" if the sample rate is $\geq 88.1$ kHz. Otherwise the output is indeterminate. Also used to set the Emphasis Audio Match feature at reset. |

| SFSEL2           | 3     | Ι    | This pin is used to selects the serial port format (SFSEL2), must be pulled up to VD through a 47 k $\Omega$ resistor.                                                                                            |

| FsSEL            | 4     | Ι    | This pin is pulled up to VD through a 47 k $\Omega$ resistor, sets the frequency of MCLK to 256Fs.                                                                                                                |

| SFSEL0           | 5     | Ι    | This pin is used to selects the serial port format (SFSEL0), must be pulled up to VD through a 47 k $\Omega$ resistor.                                                                                            |

| TX0              | 6     | 0    | Is the output of RXP0. This pin is also used to set the internal PLL at reset, must be pulled down to DGND through a 47 k $\Omega$ resistor.                                                                      |

| VDD              | 7     | Р    | Digital core power supply.                                                                                                                                                                                        |

| MCLKOU<br>T      | 8     | 0    | S/PDIF recovered master clock output from the PLL, must be connected with PIN10.                                                                                                                                  |

| SDOUT            | 9     | 0    | Audio data serial output pin. This pin must be pulled low to DGND through a 47 k $\Omega$ resistor.                                                                                                               |

| MCLKIN           | 10    | Ι    | Internal DAC master clock input port, must be connected with PIN8.                                                                                                                                                |

| <b></b> |    |   | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

|---------|----|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| QV      | 11 | 0 | Filter connection for internal quiescent voltage.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| AGND    | 12 | G | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| AOUTL   | 13 | 0 | Analog output:left channel output port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| AFILT+  | 14 | 0 | Positive reference voltage for the internal sampling circuits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| VAA     | 15 | Р | Analog power supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| AOUTR   | 16 | 0 | Analog output:right channel output port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| RXP3    | 17 | Ι | <ul> <li>Single-ended or differential receiver inputs carrying S/PDIF</li> <li>encoded digital data. The RXP[3:0] inputs comprise the 4:2</li> <li>S/PDIF Input Multiplexer. The select line control is accessed</li> <li>using the RXPSEL[1:0] pins. Unused multiplexer inputs should be</li> <li>left floating or tied to AGND.</li> <li>Single-ended or differential receiver input carrying S/PDIF</li> <li>encoded digital data. In single-ended operation this should be AC</li> <li>coupled to ground through a capacitor.</li> <li>Internal PLL power supply, +3.3 V. This power supply must be</li> <li>guaranteed low noise, insure internal PLL is stable.</li> </ul> |  |  |

| RXP2    | 18 | Ι |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| RXP1    | 19 | Ι |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| RXP0    | 20 | Ι |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| RXN     | 21 | Ι |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| VPLL    | 22 | Р |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| GND     | 23 | G | Internal PLL ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| PFILT   | 24 | 0 | PLL Loop Filter output. An RC network should be connected between this pin and pin 23.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| RST     | 25 | Ι | When RST is low, the MS8413 enters a low power mode and all<br>internal states are reset. On initial power up, RST must be held<br>low until the power supply is stable, and all input clocks are<br>stable in frequency and phase.                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| RXSEL1  | 26 | Ι | Receiver MUX Selector input - Used to select which pin,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| RXSEL0  | 27 | Ι | RXP[3:0], is used for the receiver input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| ERROR   | 28 | Ο | Receiver error indicator. When S/PDIF data is not stable or no S/PDIF input, outputs a "1". Must be pulled up to VD through a 47 k $\Omega$ resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

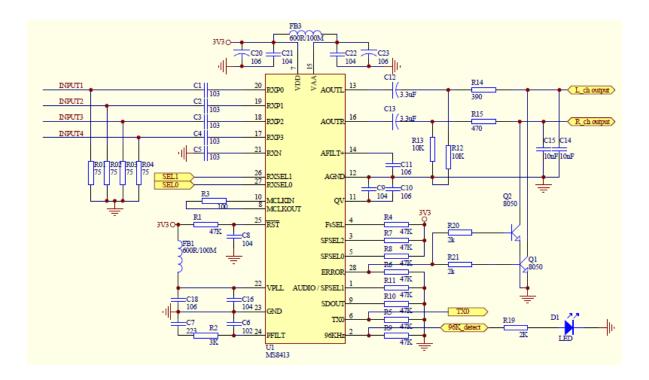

## 3、TYPICAL CONNECTION DIAGRAMS

#### Typical Connection Diagram

When the MCLK is working in jitter sensitive applications, a separate analog power supply is needed. Otherwise, the pin VAA and VDD should be connected, and the decoupling capacitor between the pin VAA and AGND is retained. The typical input structure and the recommended input circuit are detailed in "S/PDIF Receiver" and "AES3 Receiver External Components".

To get the best jitter performance, the grand of filter is directly connected to the pin AGND. See "Table 2. External PLL Component Values".

## 4、APPLICATIONS

### 4.1 Reset, Power-Down and Start-Up

When  $\overline{RST}$  is low, the MS8413 enters a low power mode and all internal states are reset, including the control port and registers, and the outputs are muted. After the PLL has settled, the serial audio outputs will be enabled.

Some options within the MS8413 are controlled by a start-up mechanism. During the reset state, some of the pins are reconfigured internally to be inputs. The pins are then switched to be outputs. This mechanism allows output pins to be used to set alternative modes in the MS8413 by connecting a 47 k $\Omega$  resistor to between the pin and either VDD (HI) or GND (LO). For each mode, every start-up option select pin must have an external pull-up or pull-down resistor as there are no internal pull-up or pull-down resistors for these start-up conditions (except for TX, which has an internal pull-down).

#### 4.2 Power Supply, Grounding, and PCB Layout

For most applications, the MS8413 can be operated from a single +3.3 V supply, following normal supply decoupling practices. For applications where the recovered input clock, output on the MCLKOUT pin, is required to be low jitter, then use a separate, quiet, analog +3.3 V supply for VAA, decoupled to AGND. Make certain that no digital traces are routed near VAA, AGND, or FILT as noise may couple and degrade performance. These pins should be well isolated from switching signals and other noise sources.

VDD sets the level for the digital inputs and outputs, as well as the AES/SPDIF receiver inputs.

Extensive use of power and ground planes, ground plane fill in unused areas and surface mount decoupling capacitors are recommended. Decoupling capacitors should be mounted on the same side of the board as the MS8413 to minimize inductance effects, and all decoupling capacitors should be as close to the MS8413 as possible.

## **5** GENERAL DESCRIPTION

The MS8413 is a monolithic CMOS device that receives and decodes audio data according to the AES3, IEC60958, S/PDIF, and EIAJ CP1201 interface standards. The MS8413 accepts data at standard audio sample rates including 48, 44.1 and 32 kHz in SSM, 96, 88.2 and 64 kHz in DSM, and 192, 176.4 and 128 kHz in QSM.

The MS8413 provides an 4:1 multiplexer to select between four inputs for decoding and to allow an input signal to be routed to an output of the MS8413. Input data can be either differential or single-ended. A low jitter clock is recovered from the incoming data using a PLL. The decoded audio data is output through a configurable, 3-wire serial audio output port.

MS8413 dedicated pins are used to select audio stream inputs for decoding and transmission to a dedicated TX pin, also provides channel status and user data output pins.

#### 5.1 AES3 and S/PDIF Standards Documents

This document assumes that the user is familiar with the AES3 and S/PDIF data formats. It is advisable to have current copies of the AES3, IEC60958, and IEC61937 specifications on hand for easy reference.

The latest AES3 standard is available from the Audio Engineering Society or ANSI at www.aes.org or at www.ansi.org. Obtain a copy of the latest IEC60958/61937 standard from ANSI or from the International Electrotechnical Commission at www.iec.ch. The latest EIAJ CP-1201 standard is available from the Japanese Electronics Bureau.

**Application Note :** Overview of Digital Audio Interface Data Structures contains a useful tutorial on digital audio specifications, but it should not be considered a substitute for the standards.

#### 5.2 AES3/SPDIF Receiver

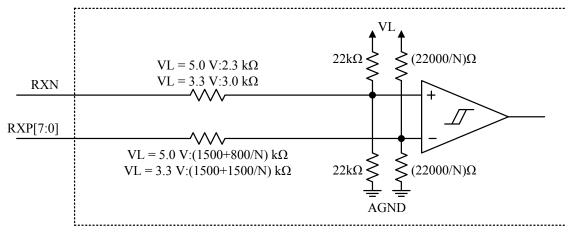

The MS8413 includes an AES3/SPDIF digital audio receiver. The receiver accepts and decodes bi-phase encoded audio and digital data according to the AES3, IEC60958 (S/PDIF), and EIAJ CP-1201 interface standards. The receiver consists of an analog differential input stage, driven through analog input pins RXP0 to RXP3 and a common RXN, A PLL based clock recovery circuit, and a decoder which separates the audio data from the channel status and user data. External components are used to terminate the incoming data cables and isolate the MS8413. Figure shows the input structure of the receiver.

If RXP[7:0] is selected by either the receiver MUX or the TX passthrough MUX,N=1. If RXP[7:0] is selected by both the receiver MUX and the TX passthrough MUX,N=2. If RXP[7:0] is not selected at all,N=0(i.e. high impedance).

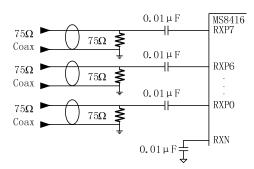

The MS8413 employs a 4:1 S/PDIF input multiplexer to accommodate up to eight channels of input digital audio data. Digital audio data may be single-ended or differential. Differential inputs utilize RXP[3:0] and a shared RXN. Single ended signals are accommodated by using the RXP[3:0] inputs and AC coupling RXN to ground. All active inputs to the MS8413 4:1 input multiplexer should be coupled through a capacitor as these inputs are biased at VDD/2 when selected. These inputs are floating when not selected. Unused multiplexer inputs should be left floating or tied to AGND. The recommended capacitor value is 0.01  $\mu$ F to 0.1  $\mu$ F. The recommended dielectrics for the AC

coupling capacitors are C0G or X7R.

The input voltage range for the input multiplexer is set by the I/O power supply pin, VDD. The input voltage of the RXP[3:0] and RXN pins is also set by the level of VDD. Input signals with voltage levels above VDD or below GND may degrade performance or damage the part.

## 5.3 Hardware Mode

In Hardware Mode the input to the decoder is selected by dedicated pins, RXSEL[1:0]. Selectable inputs are restricted to RXP0 to RXP3 for both the receiver and the TX output pin. RXSEL1=0, RXSEL0=0, select RXP0.

RXSEL1=0, RXSEL0=1, select RXP1.

RXSEL1=1, RXSEL0=0, select RXP2.

RXSEL1=1, RXSEL0=0, select RXP3.

#### 5.4 Clock Recovery and PLL Filter

Please see "PLL Filter" for a general description of the PLL, selection of recommended PLL filter components, and layout considerations.

## 5.5 Error And Status Reporting

While decoding the incoming bi-phase encoded data stream, the MS8413 has the ability to identify various error conditions.

In Hardware Mode, the user may only choose between Non-Validity Receiver Error (NVERR) or Receiver Error (RERR) by pulling the NV/RERR pin low or high, respectively. The pull-up/pull-down condition will be sensed on start-up, and the appropriate error reporting will be set.

RERR – The previous audio sample is held and passed to the serial audio output port if the validity bit is high, or a parity, bi-phase, confidence or PLL lock error occurs during the current sample.

NVERR – The previous audio sample is held and passed to the serial audio output port if a parity, bi-phase, confidence or PLL lock error occurs during the current sample.

#### 5.6 Non-Audio Detection

An AES3 data stream may be used to convey non-audio data, thus it is important to know whether the incoming AES3 data stream is digital audio or not. This information is typically conveyed in channel status bit 1, which is extracted automatically by the MS8413. However, certain non-audio sources, such as AC-3<sup>TM</sup> or MPEG encoders, may not adhere to this convention, and the bit may not be properly set. The MS8413 AES3 receiver can detect such non-audio data through the use of an autodetect module.

If the AES3 stream contains sync codes in the proper format for IEC61937 or DTS<sup>®</sup> data transmission, an internal AUTODETECT signal will be asserted. If the sync codes no longer appear after a certain amount of time, autodetection will time-out and AUTODETECT will be de-asserted until another format is detected.

$\overline{AUDIO}$  is output on pin 1. If non-audio data is detected, the data is still processed exactly as if it were normal audio. The exception is the use of de-emphasis auto-select feature which will bypass the de-emphasis filter if the input stream is detected to be non-audio. It is up to the user to mute the outputs as required.

#### 5.7 Channel Status And User-Data Handling

Received Channel Status (C), and User (U) bits are output on pins 5 and 4.

#### 5.8 AES3 Receiver External Components

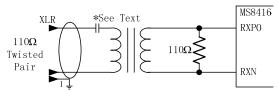

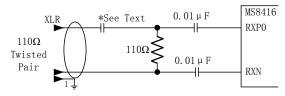

The MS8413 AES3 receiver is designed to accept both the professional and consumer interfaces. The digital audio specifications for professional use call for a balanced receiver, using XLR connectors, with  $110 \ \Omega \pm 20\%$  impedance. The XLR connector on the receiver should have female pins with a male shell. Since the receiver has a very high input impedance, a  $110 \ \Omega$  resistor should be placed across the receiver terminals to match the line impedance, as shown in Figures 1 and 2. Although transformers are not required by the AES specification, they are strongly recommended.

If some isolation is desired without the use of transformers, a 0.01  $\mu$ F capacitor should be placed in series with each input pin (RXP[3:0] and RXN) as shown in Figure 2. However, if a transformer is not used, high frequency energy could be coupled into the receiver, causing degradation in analog performance.

Figures 1 and 2 show an optional (recommended) DC blocking capacitor (0.1  $\mu$ F to 0.47  $\mu$ F)

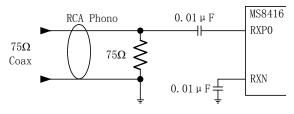

in series with the cable input. This improves the robustness of the receiver, preventing the saturation of the transformer, or any DC current flow, if a DC voltage is present on the cable. In the case of the consumer interface, the standards call for an unbalanced circuit having a receiver impedance of 75  $\Omega \pm 5\%$ . The connector for the consumer interface is an RCA phono socket. The receiver circuit for the consumer interface is shown in Figure 3. An implementation of the Input S/PDIF Multiplexer using the consumer interface is shown in Figure 4.

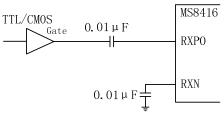

The circuit shown in Figure 5 may be used when external RS422 receivers, optical receivers or other TTL/CMOS logic outputs drive the MS8413 receiver section.

In the configuration of systems, it is important to avoid ground loops and DC current flowing down the shield of the cable that could result when boxes with different ground potentials are connected. Generally, it is good practice to ground the shield to the chassis of the transmitting unit, and connect the shield through a capacitor to chassis ground at the receiver. However, in some cases it is advantageous to have the ground of two boxes held to the same potential, and the cable shield might be depended upon to make that electrical connection. Generally, it is a good idea to provide the option of grounding or capacitively coupling the shield to the chassis.

#### **5.9 Isolating Transformer Requirements**

Please refer to the application note: AES and SPDIF Recommended Transformers for resources on transformer selection.

Figure 1. Professional Input Circuit

Figure 3. Consumer Input Circuit

Figure 5. TTL/CMOS Input Circuit

#### 5.10 PLL Filter

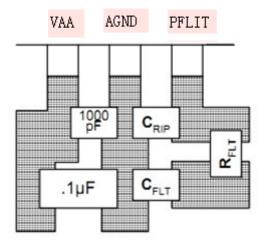

Board layout and capacitor choice affect each other and determine the performance of the PLL. Figure 6 contains a suggested layout for the PLL filter components and for bypassing the analog supply voltage. The 0.1  $\mu$ F bypass capacitor is in a 1206 form factor. R<sub>FLT</sub>, C<sub>FLT</sub>, C<sub>RIP</sub>, and the 1000 pF decoupling capacitor are in an 0805 form factor. The traces are on the top surface of the board with the IC so that there is no via inductance. The traces themselves are short to minimize the inductance in the filter path. The VAA and AGND traces extend back to their origin and are shown only in truncated form in the drawing.

Figure 6. Recommended Layout Example The external PLL component values are listed in Table 2. Table 2. External PLL Component Values

| Range (kHz) | R <sub>FLT</sub> | C <sub>FLT</sub> | C <sub>RIP</sub> | Settling Time |

|-------------|------------------|------------------|------------------|---------------|

| 32 - 192    | 2kΩ              | 22nF             | 1nF              | 4ms           |

#### 5.11 Jitter Attenuation

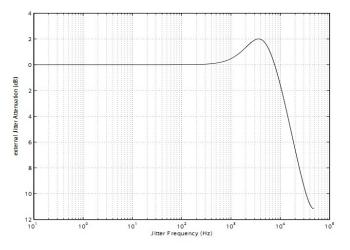

Shown in Figure 7 is the jitter attenuation plot. The AES3 and IEC60958-4 specifications state a maximum of 2 dB jitter gain or peaking.

Figure 7. Jitter Attenuation Characteristics of PLL

#### 5.12 De-Emphasis

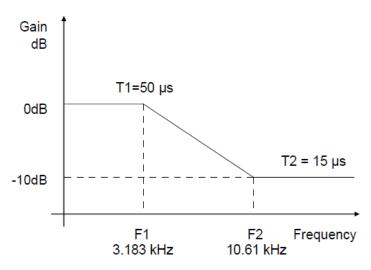

The MS8413 includes on-chip digital de-emphasis. Figure 8 shows the de-emphasis curve for Fs equal to 44.1 kHz.

Figure 8. De-Emphasis Curve (Fs = 44.1kHz)

#### 5.13 Analog Output Initialization and Power-Down

The MS8413 enters the Power-Down State upon initial power-up. The interpolation filters and delta-sigma modulators are reset, and the internal voltage reference, multi-bit digital-to-analog converters and switched-capacitor low-pass filters are powered down. The device will remain in the Power-down mode until MCLK is present. Power is then applied to the internal voltage reference. Finally, power is applied to the D/A converters and switched-

capacitor filters, and the analog outputs will ramp to the quiescent voltage VQ.

### 5.13.1 Output Transient Control

The MS8413 uses Popguard technology to minimize the effects of output transients during power-up and power-down.

- (1) Power-Up: When the device is initially powered-up, the audio outputs, AOUTL and AOUTR, are clamped to VQ which is initially low. After MCLK is applied the outputs begin to ramp with VQ towards the nominal quiescent voltage. This ramp takes approximately 250 ms with a 3.3  $\mu$ F cap connected to VQ (420 ms with a 10  $\mu$ F connected to VQ) to complete.

- (2) To prevent audio transients at power-down the DC-blocking capacitors must fully discharge before turning off the power. In order to do this MCLKIN should be stopped for a period of about 250 ms for a 3.3  $\mu$ F cap connected to VQ (420 ms for a 10  $\mu$ F cap connected to VQ) before removing power. During this time voltage on VQ and the audio outputs discharge gradually to GND.

### 5.13.2 Analog Output and Filtering

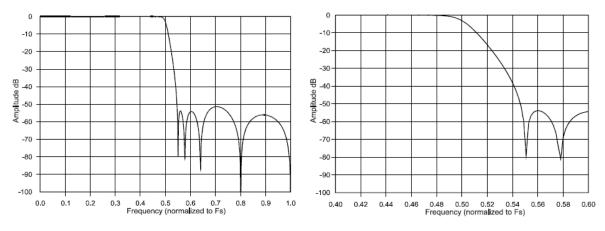

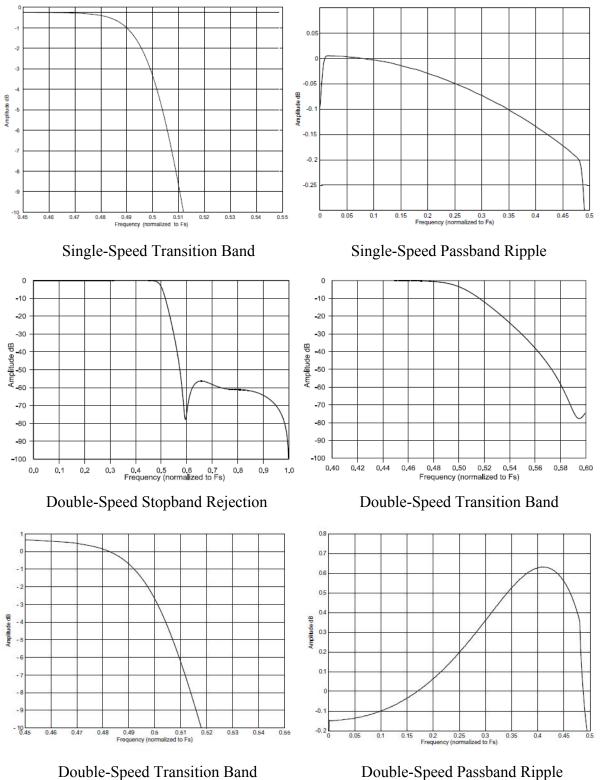

The analog filter present in the MS8413 is a switched-capacitor filter followed by a continuous time low pass filter. Its response, combined with that of the digital interpolator, is given in Figures.

Single-Speed Stopband Rejection

Single-Speed Transition Band

**Double-Speed Passband Ripple**

Quad-Speed Transition Band

## PACKAGE OUTLINE DIMENSIONS