目次

はじめに

研究室でのFPGAソフトの使い方も兼ねている記事です。初心者すぎて、これであっているのかマジでわかりませんが、とりあえずシミュレーションも含めて動きました。

最新のシミュレーションソフトであるQuestaのライセンス取得と更新がめんどくさいし、何故か起動しないので、昔のModelSimを使うようにします。

頑張って、最新のQuartusとModelSimを組み合わせていますが、初めからQuartusの20.1.1をインストールすればよかったです。

昔はマルツで安く売られていたCYCLONE(EP1C3T100C8N)を使用していたのですが、発売が終了してしまったので、新たにインテル® MAX® 10 - 10M08 評価キットを(研究室で)買いました。ソフトがQuartus IIから最新のQuartus Liteに変わり、いろいろ変わっていたので基本的な使い方を探りました。

ソフトのダウンロード

最新のQuartusとModelSimを組み合わせて使用するなら、上2つをダウンロード

ModelSimが同梱されている旧バージョンのQuartusをダウンロードするなら、[おすすめ]のやつをダウンロード

Quartus Prime Lite Editionが無料で使用できるのでこれをダウンロードします。2024/10/2現在の最新バージョンは23.1.1です。

Intel® Quartus® Prime Lite Edition Design Software

シミュレーションソフトである、ModelSimです。最終バージョンが20.1.1です。これ以降はQuestaにバトンタッチしています。

ModelSim-Intel® FPGAs Standard Edition Software Version 20.1.1

[おすすめ]

Questaでなくライセンスが不要なModelSimが初めから同梱されている古いバージョンであるQuartus Prime Lite Edition 20.1.1はここからダウンロードできます。

Intel® Quartus® Prime Lite Edition Design Software Version 20.1.1 for Windows

ソフトのインストール

Quartus Prime Lite Edition 20.1.1をインストールした場合は関係ないです。普通に全部インストールすればいいともいます。

Quartusの方は特にいじることもなく、ほとんどそのままインストールしました。Questaもインストールしましたが、しなくてもよかったかもしれません。

ModelSimの方もなにもいじらずにインストールしました。エディションは無料であるStarterを選択します。後で、インストールパス(ディフォルトはC:\intelFPGA\20.1)を使用するシーンがあるので覚えておいた方がいいです。

初期セットアップ

Quartus Prime Lite Edition 20.1.1をインストールした場合は不要です。

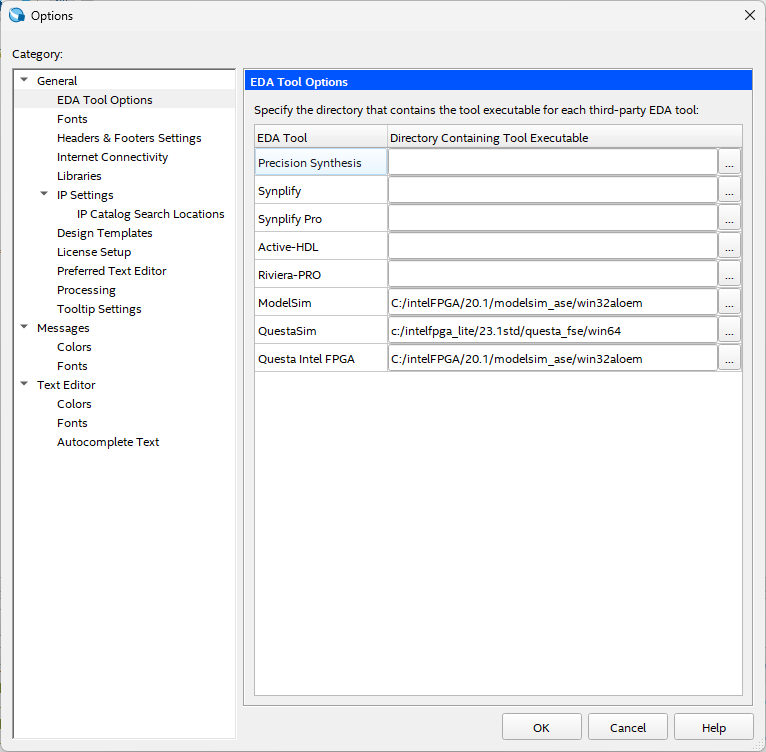

Questaではなく、ModelSimを使うように設定が必要です。Quartusを開いて、ツールバーのTool→Options→EDA Tool Optionsを開いて、ModelSimのところに、modelsim.exeが存在するフォルダのパスを入力します。パスは、ModelSimのインストールパス\modelsim_ase\win32aloem

です。パスをいじっていなければ、C:/intelFPGA/20.1/modelsim_ase/win32aloem

です。その後に、Questa Intel FPGAの入っている値をQuestaSimのところにコピペして、ModelSimのパスをQuesta Intel FPGAにコピペします。

Lチカ(PWM)をする方法

1. プロジェクトの作成

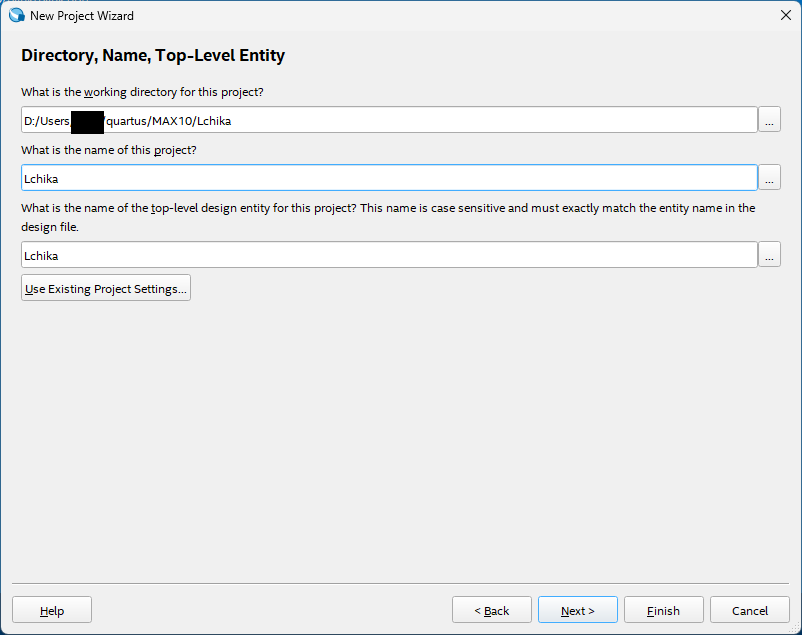

1-1. New Project Wizardを押します。

1-2. Projectの保存場所と名前を決めます。

1-3. Empty projectを選択する

1-4. Add Filesは何も選ばずにNext

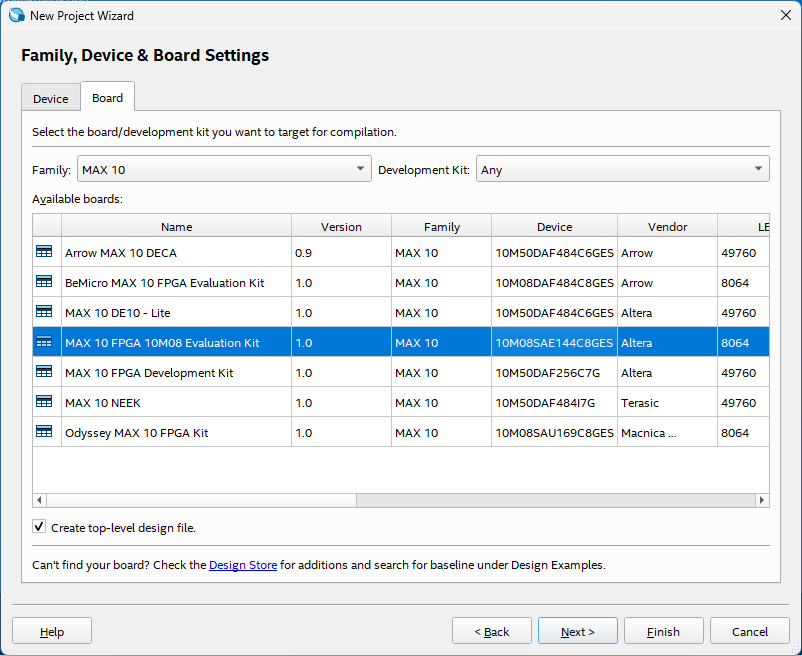

1-5. ボードを選択します。

Boardタブで、使用しているMAX 10 FPGA 10M08 Evalution Kitを選択します。

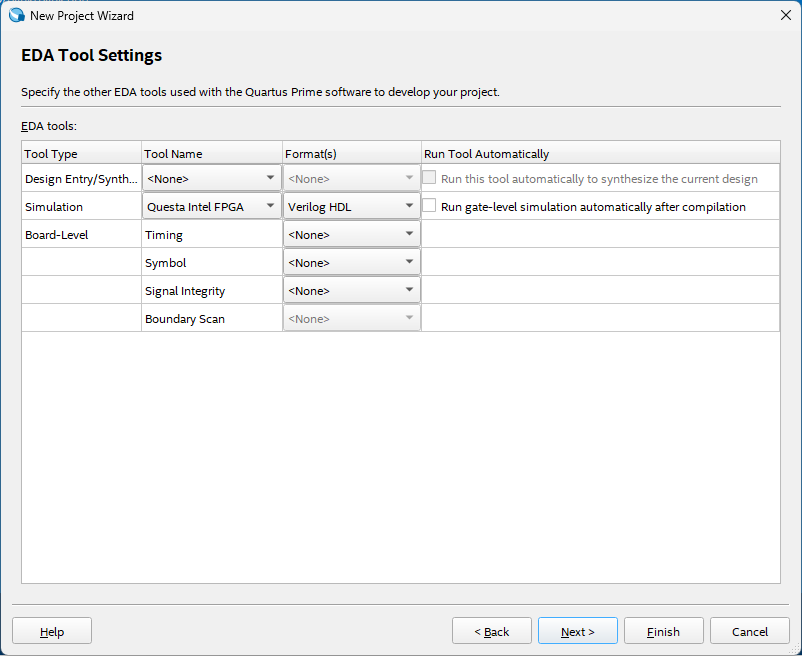

1-6. EDA Tool Settingsはこんな感じにしました。

Quartus 20.1の場合だと、SimulationのToolNameの欄はModelSimに設定すれ良いと思います。

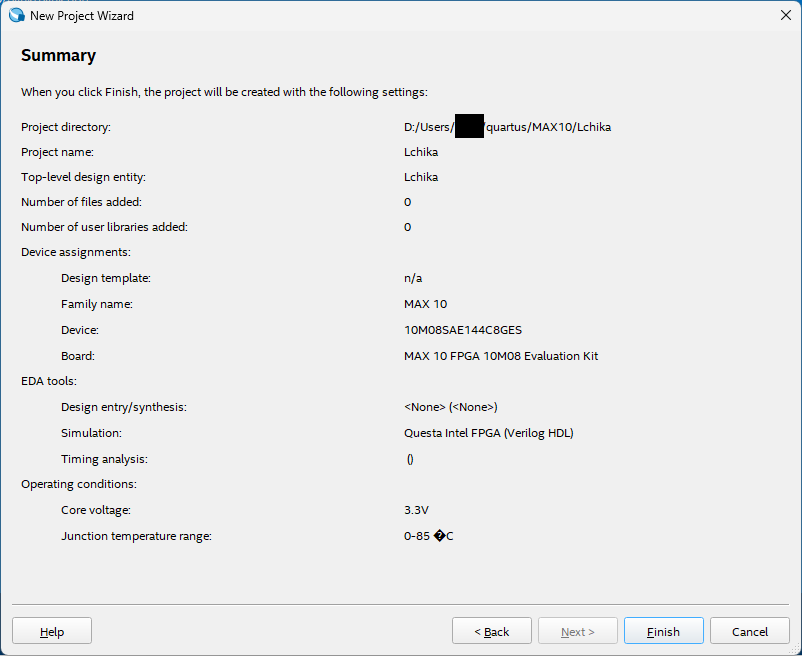

1-7. Summaryで確認

合ってたらFinishです。

2. Verilogの記述

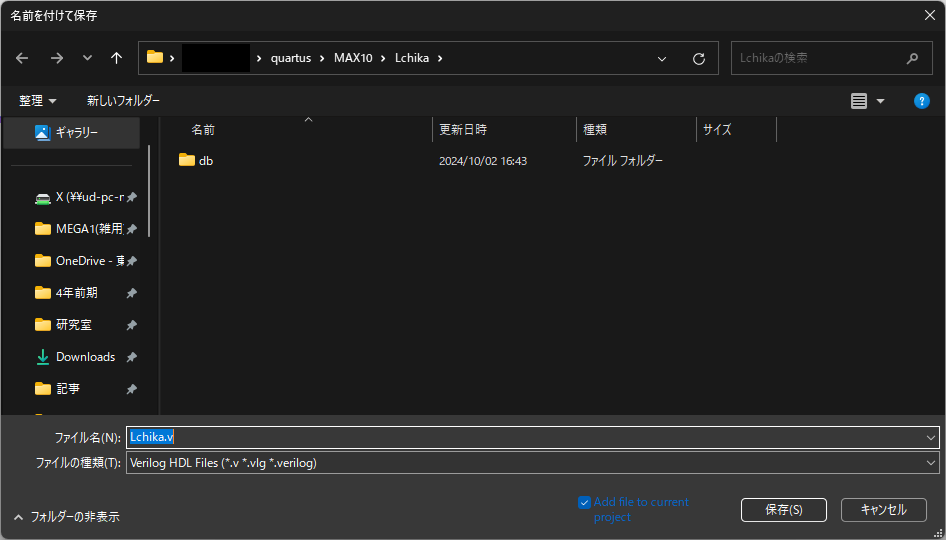

2-1. ファイルを作成

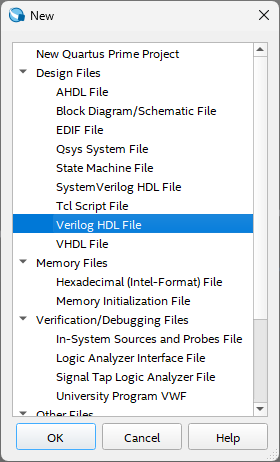

File→New→Design Files→Verilog HDL FileでOK

2-2. コードを書く

1秒ごとについたり消えたりするコードはこんな感じです。かなりゴリ押しで50MHzを1/100,000,000分周して0.5Hzを作成しています。FPGAのクロック周波数は回路図(公式(zipファイル)、ミラー(pdf))で確認ができます。

// 0.5Hz Duty50%を作りたい

// FPGAのクロックは50MHz(27番ピン)

// 1/100,000,000

// 0~49,999,999、50,000,000~99,999,999

// 100,000,000<134,217,727=27bit

module sig01 (

input clk,

output reg sig01

);

reg [26:0] t = 0;

reg y = 1;

always @(posedge clk) begin

if (t <= 49999999)

y = 1;

else if (50000000 <= t && t <= 99999999)

y = 0;

t = t + 1;

if (t == 100000000)

t = 0;

sig01 = y;

end

endmodule10kHzデューティー比30%の時のコードだとこんな感じです。

// 10kHz Duty30%を作りたい

// FPGAのクロックは50MHz(27番ピン)

// 1/5000

// 0~1499は1、1500~4999は0

// 4999<8191=13bit

module sig01 (

input clk,

output reg sig01

);

reg [13:0] t = 0;

reg y = 1;

always @(posedge clk) begin

if (t <= 1499)

y = 1;

else if (1500 <= t && t <= 4999)

y = 0;

t = t + 1;

else if (t == 5000)

t = 0;

sig01 = y;

end

endmodule2-3. 保存する

おまけ

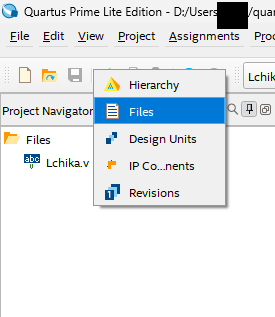

Project NavigatorをHierarchyからFilesにすると保存したファイルが一覧で見れて、見やすい

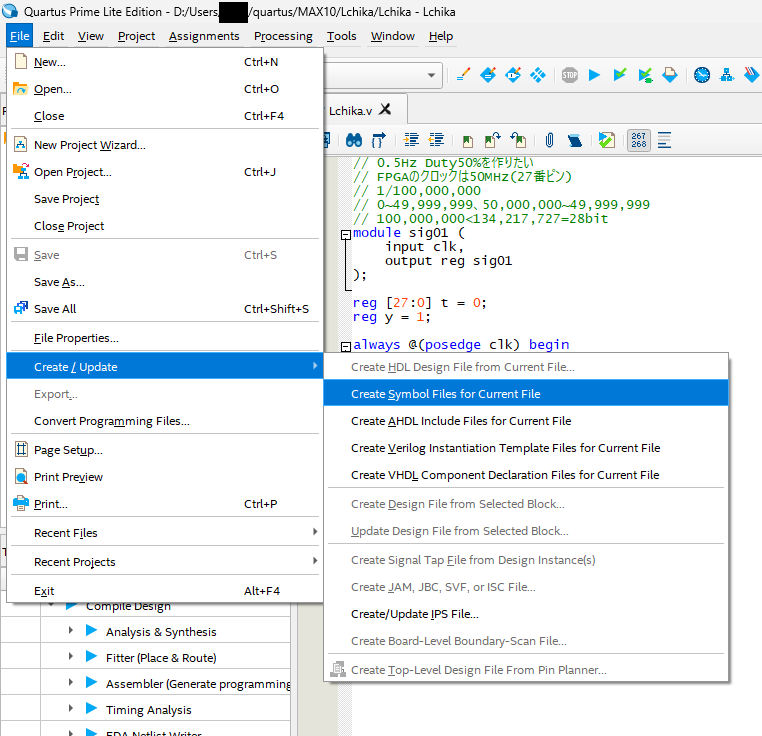

2-4. シンボルの作成

File→Create/Uploade→Create Symbol Files for Current Fileを押して、シンボルファイルを作成する

Verilogに文法エラーがあると、このときに怒られる

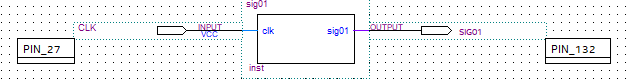

3. ブロックの配置

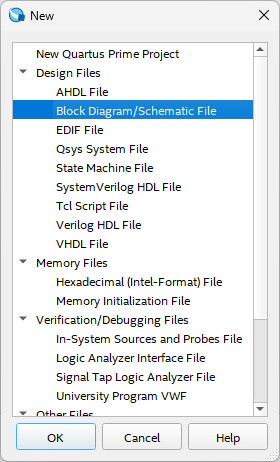

3-1. ファイルを作成

File→New→Design Files→Block Diagram/Schematic FileでOKです。ファイル名は先ほど作成したモジュールとは違うものにしてください。

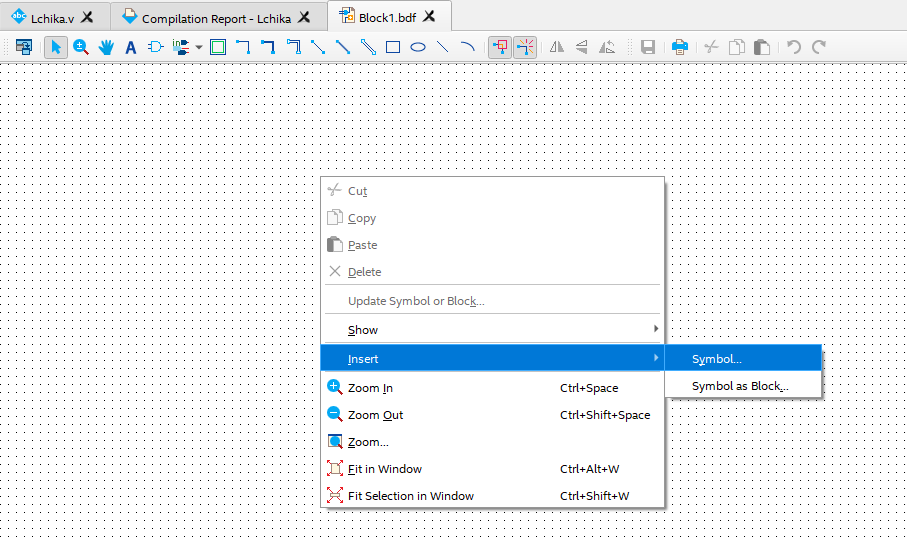

3-2. ブロック挿入

ドットの上で適当に右クリックしてInsert→Symbol...を押します。

3-3. ブロックを選択

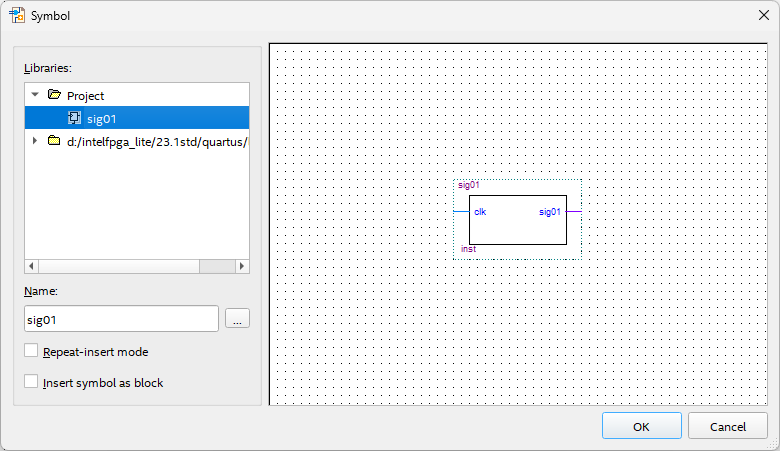

Projectフォルダの中に、先程作成したモジュールが入っているのでOK。適当な場所にクリックして配置します。

3-4. inputピンを選択

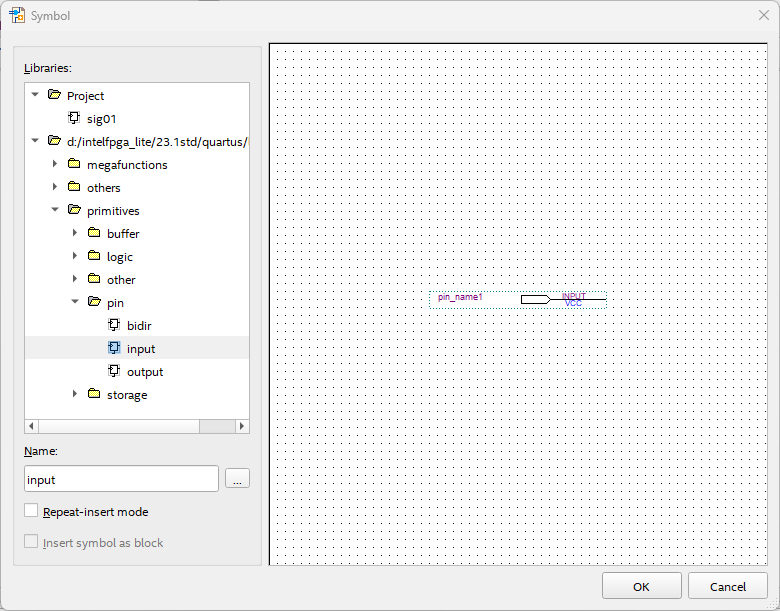

同じ手順でドットの上で適当に右クリックしてInsert→Symbol...を押します。c:/intel・・・/libraries/→primitives→pin→inputを選択します。

3-5. inputピンを配置

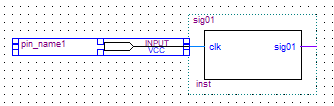

clkは入力なので、そこにつながる様にピンを置きます。

3-6. outputピンを配置

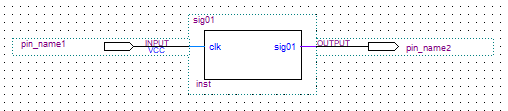

3-4、3-5と同様の手順で、sig01にoutputピンを配置します。

3-7. ピンの名前を適当につける

inputのブロック、outputのブロックの上で右クリックしてPropertiesでピンの名前を設定できます。

3-8. 保存する

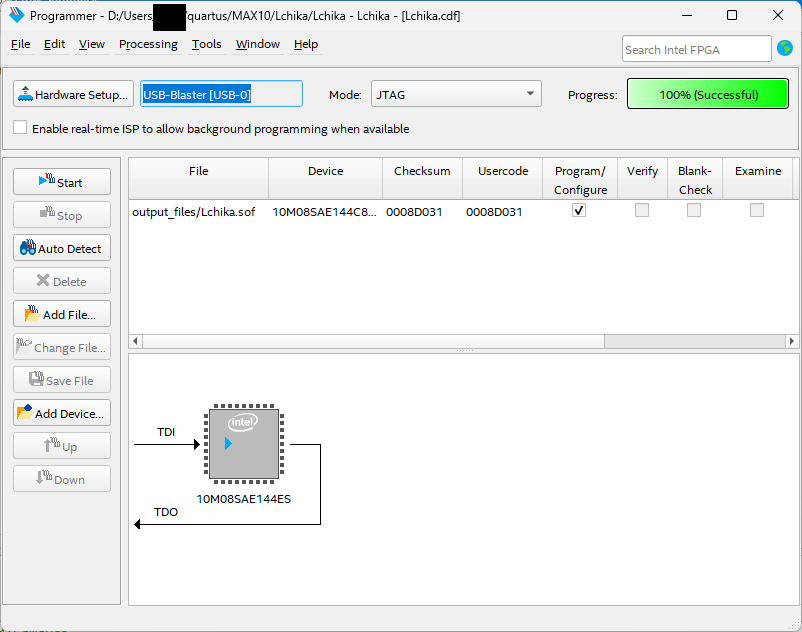

4. コンパイル

4-1. Top-level designを設定する

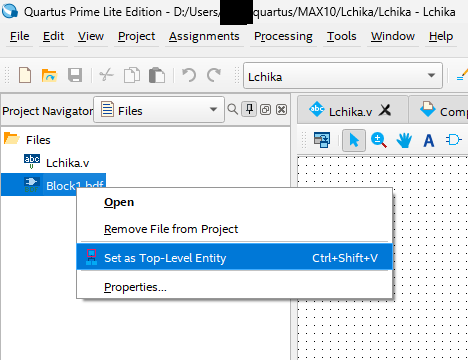

そのままコンパイルしようとすると、Error (12007): Top-level design entity "Lchika" is undefinedと言われるので、Top-level designを設定します。

右側のProject NavigatorをFilesにした後、先程保存したbdfファイルを右クリックしてSet as Top-Level Entityをクリックします。

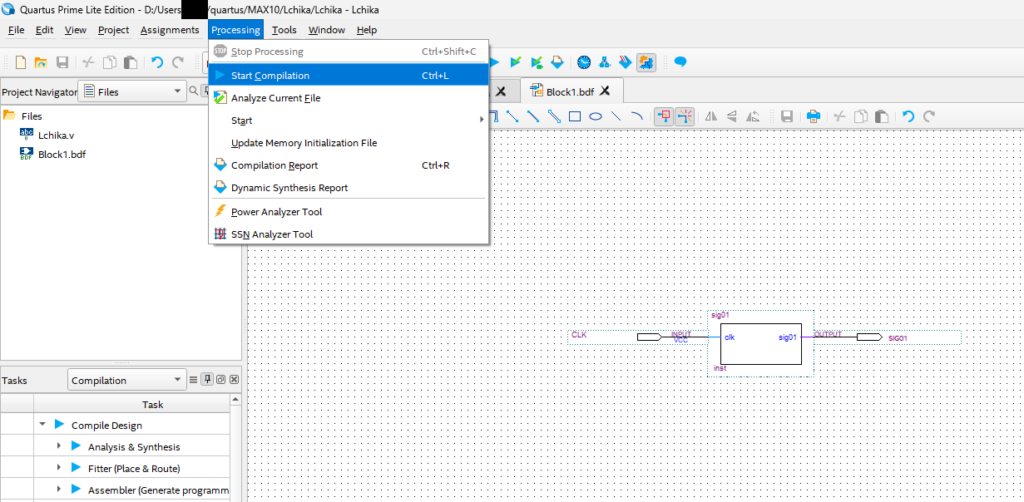

4-2. Processing→Start Compilationを実行

何か間違えているとここでエラーが出ます。

4-3. コンパイルが終わると、Tasksのところが%表示からチェックマークに変わるはずです。

5. シミュレーション

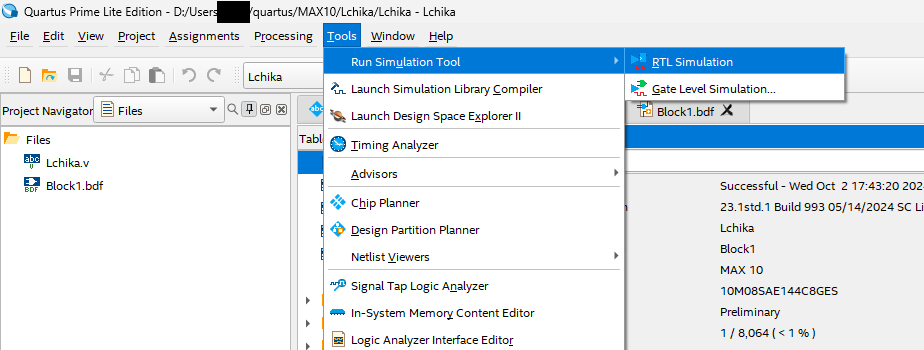

5-1. シミュレーションソフト(ModelSim)の起動

Tools→Run Simulation Tool→RTL Simulationを押して起動します。

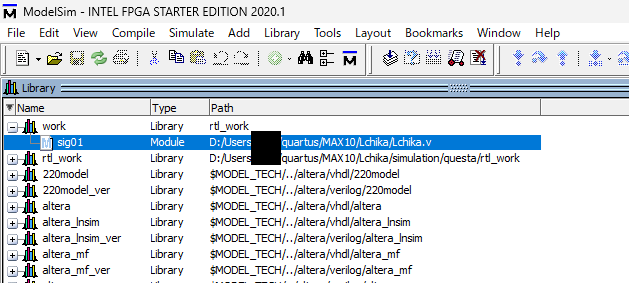

5-2. ファイルを開く

workの中に、モジュールのファイルがあります。それをダブルクリックします。

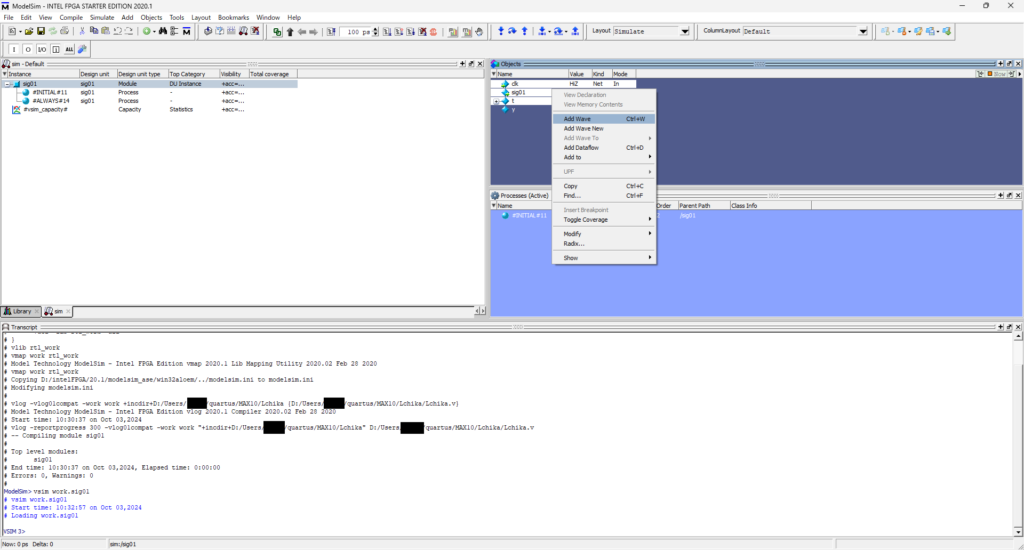

5-3. 右側のObjectsのところに、入力ピン、出力ピン、内部レジスタが出てきます。この中で観測したいものを選択(Ctrlキー)を押しながらクリックし、Add Waveをクリックします。

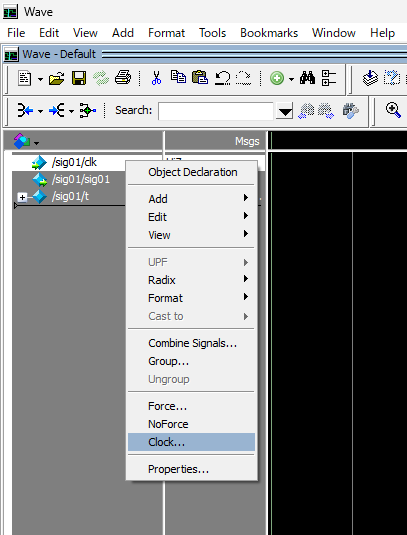

5-4. Waveウィンドウのclkピンを右クリックし、Clockをクリックします。

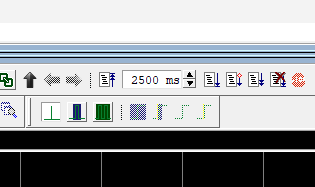

5-5. クロック信号は50MHzなので、「20 ns」と入力し、OK

5-6. シミュレーション時間をLチカの場合は「2500 ms」に設定、10kHzのPWMとかであれば、150 usとかがいいと思います。

5-7. 時間設定の隣りにある、Runボタンを押すとシミュレーションが始まります。2500 msだとかなり時間がかかります。ウィンドウの下の方に、Now:秒数 って感じで進捗が出ます。

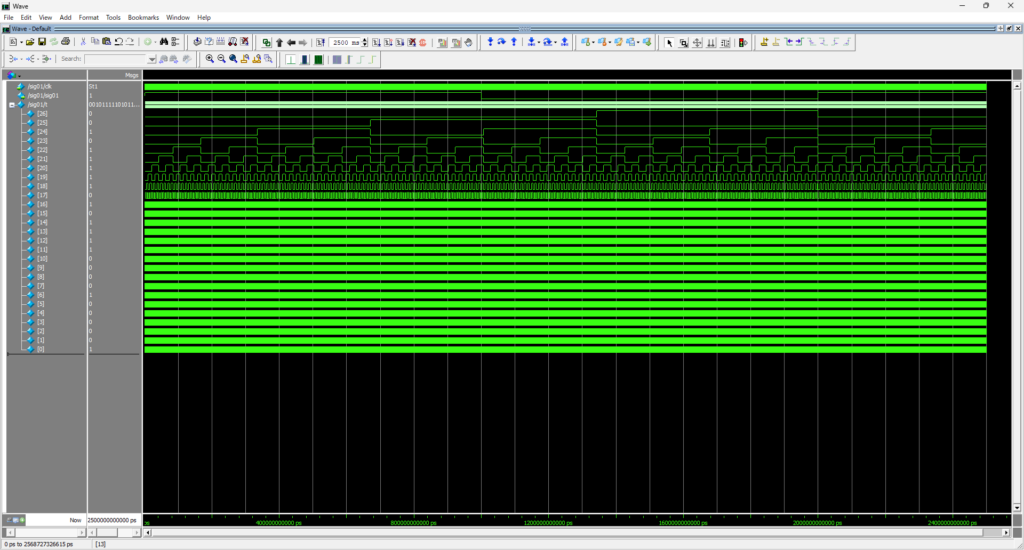

5-8. シミュレーション完了

正しく動作しているか確認してください。修正する場合は、ピンの増減がなければVerilogファイルを修正し、再度コンパイルすれば良いと思います。ピンの増減があるなら、シンボルの作成とブロックの配置もする必要があるかもしれません。

6. ピンの割り当て

6-1. シミュレーションソフト(ModelSim)を閉じて、Quartusに戻ります。

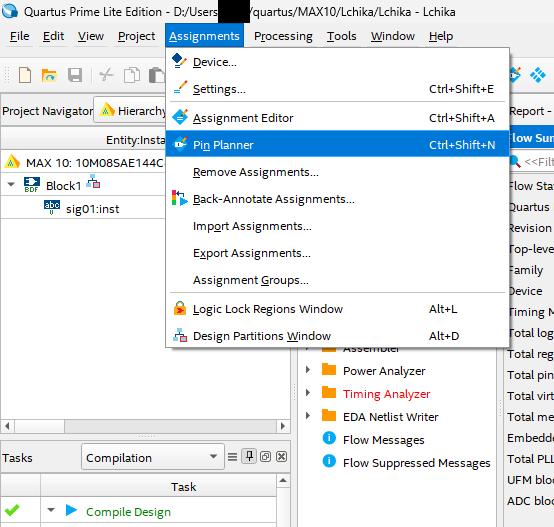

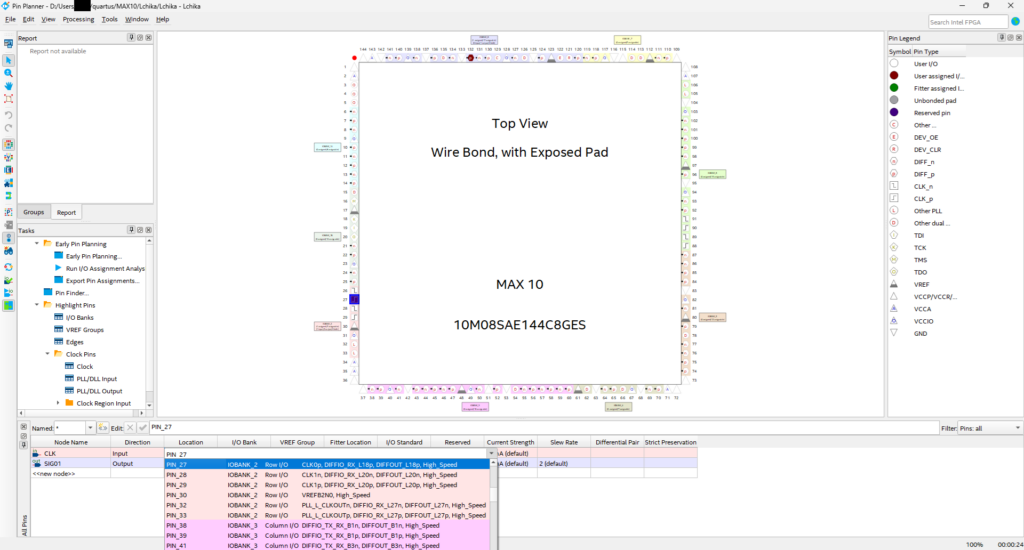

6-2. Assignments→Pin Plannerを押します。

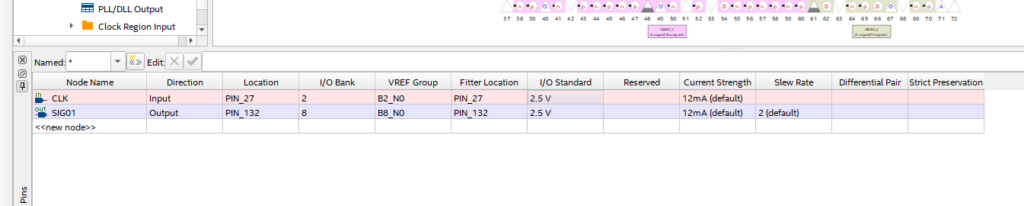

6-3. 下の方に割り当てるピンが出てくるので、Locationのところでピンを選択します。

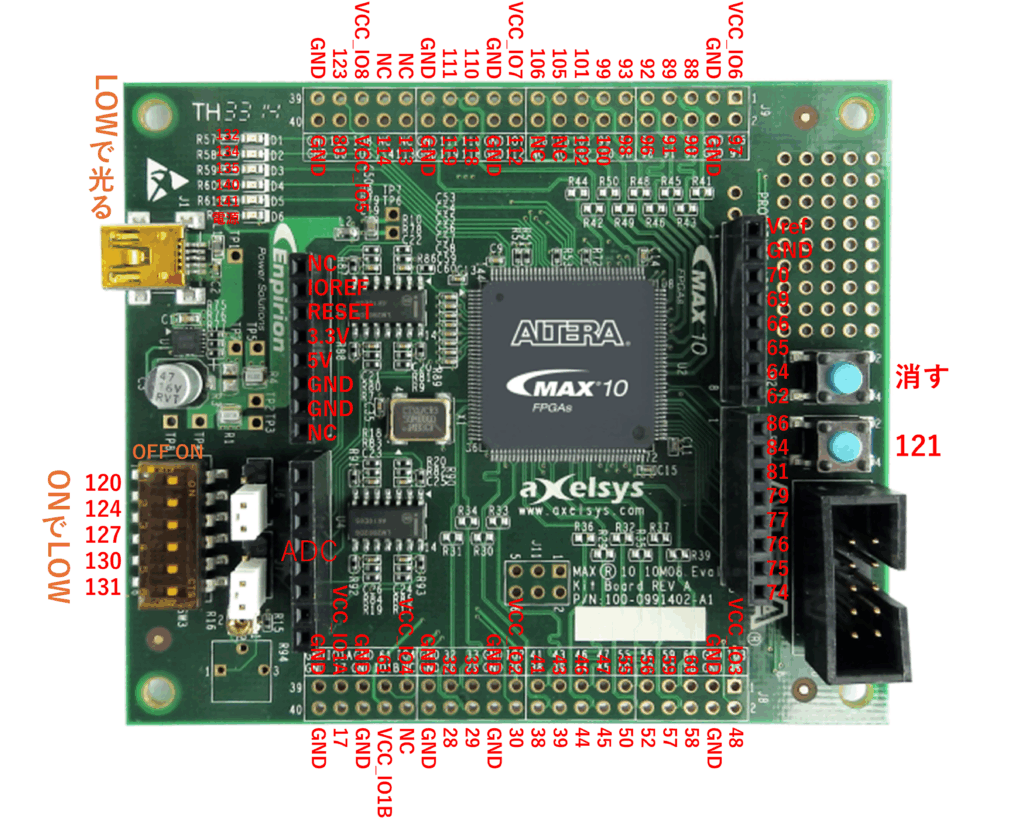

ボードのパッドとFPGAのピン番号の関係は以下の様になっています

詳しくは回路図(公式(zipファイル)、ミラー(pdf))で確認ができます。

クロックのピン番号は27なので、PIN_27を選択します。Lチカの場合、LED1のピンがPIN_132です。それ以外の項目はdefaultでいいと思います。ピンの出力電圧や最大電流の調整もここでできます。

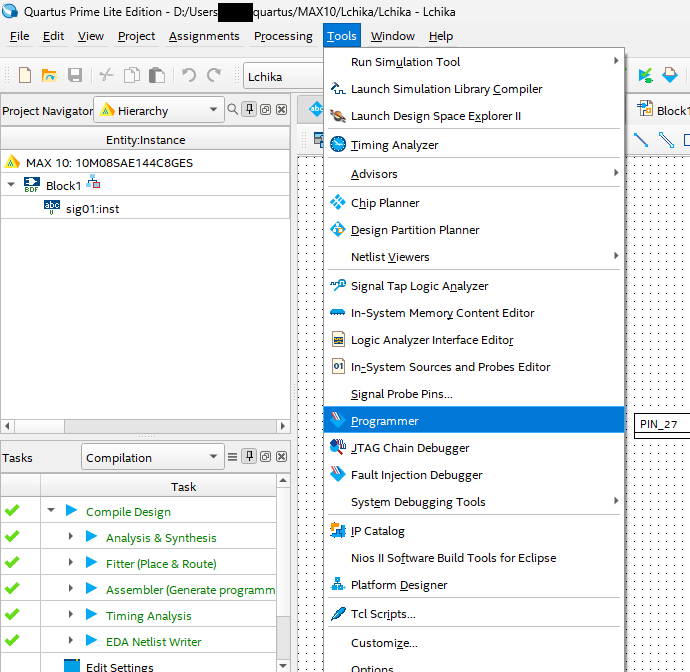

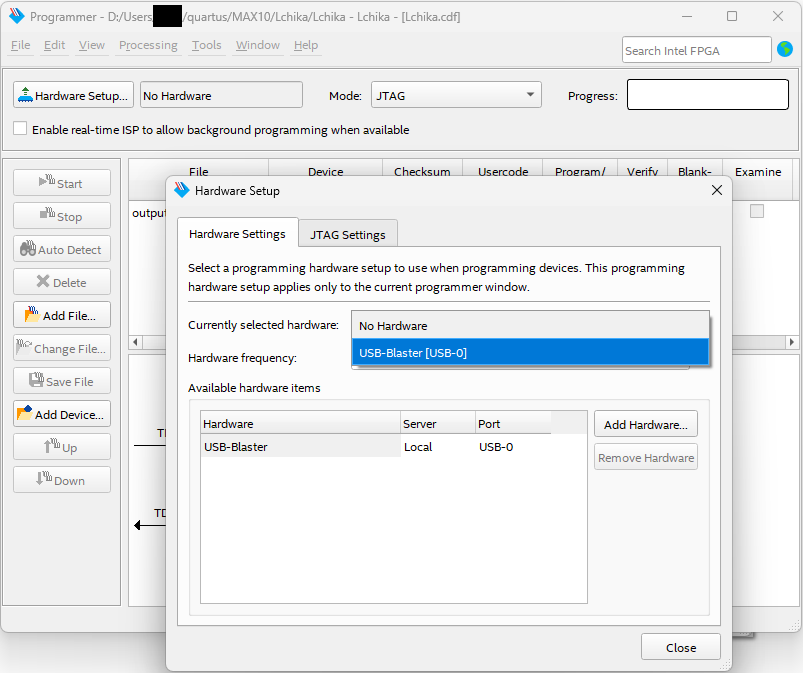

7. 書き込み

7-1. ピンの割り当てができたら、再度コンパイルを行います。コンパイル後にブロックファイルを確認すると、ピンのブロックの下にピンが表示されます。

7-2. Tools→Programmerを押します。

7-3. USB-BlasterをPCに挿し、FPGAの電源を入れる。(既に行っている場合は不要)

7-4. Hardware Setupを押して、Currently selected hardwareでUSB-Blaseterを選択する。

もし、挿しているのにもかかわらず表示されないのであれば、ドライバが刺さっていません。

マクニカ「USB-Blaster™ のドライバーをインストールしてみよう」を参考にインストールしてください。

7-5. Startを押して、Progressが100%(Successful)になったら書き込み完了です。

結果

Lチカできた!

正真正銘Lチカできた!

— Unagi Dojyou (@Unagi_Dojyou) October 2, 2024

シミュレーションソフトは動かないQuestaじゃなくてModelSimを使うようにした pic.twitter.com/MhmO4SUyxy

終わりに

シミュレーションソフトの使い方が訳わからなくて割と大変でした。無事に使えるようになったので、研究にバリバリ使っていくことにします。

VWFシミュレーション、簡単なロジックを確認するのに重宝してたんですが、

ver23になってから、そのままでは使えず困ってたんですよね。

助かりました。ありがとうございました。